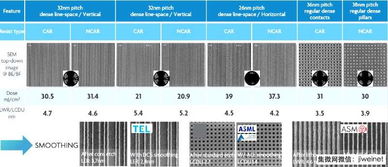

可用于埃米节点,首次展示功能性单片器件

当地时间6月18日,imec(比利时微电子研究中心)通过官网宣布,在本周举行的2024年IEEEVLSI技术与电路研讨会(2024VLSI)上,imec首次展示了具有堆叠底部和顶部源/漏极触点的功能性单片CMOSCFET器件。虽然结果是从正面图案化两个触点获得的,但imec还展示了将底部触点形成移至晶圆背面的可行性——将顶部器件的存活率从11%显著提高到79%。

imec的逻辑技术路线图设想在A7(7埃米)制程节点设备架构中引入互补场效应晶体管(CFET)。当与先进的布线技术相结合时,CFET有望将标准单元轨道高度从5T降低到4T甚至更低,而不会降低性能。在集成n和pMOS垂直堆叠结构的不同方法中,与现有的纳米片型工艺流程相比,单片集成被认为是破坏性最小的。

△图1:具有MDI和堆叠正面图案化触点的CMOSCFET器件(TC=顶部触点;TJ=顶部结;BC=底部触点;BJ=底部结)。SEM横截面沿BC/TC(左)和横跨BC/TC(右)显示。

△图2:具有正面图案化堆叠接触的nFET和pFET的ld/Vg曲线。

△图3:SEM图片显示在晶圆背面形成的底部触点,并且准确定位在正面形成的底部结上方(BDI=底部电介质隔离)。

在2024年VLSI研讨会上,imec首次展示了具有堆叠顶部和底部触点的功能性单片CMOSCFET器件。CFET集成在18nm栅极长度、60nm栅极间距和n和p器件之间50nm的垂直间隔中。在测试载体上演示了电气功能,其中nFET和pFET器件使用公共栅极,顶部和底部触点从正面连接。

所提出的工艺流程包括两个CFET特定模块:中间电介质隔离(MDI)以及堆叠的底部和顶部触点。

MDI是imec首创的一种模块,用于隔离顶栅和底栅,并区分n型和p型器件之间的阈值电压设置。MDI模块基于对CFET“有源”多层Si/SiGe堆栈的修改,并允许内部间隔物的共集成–这是一种纳米片特有的功能,可将栅极与源极/漏极隔离。imecCMOS器件技术总监NaotoHoriguchi表示:“我们采用MDI优先方法获得了最佳工艺控制结果,即在源极/漏极凹槽之前–在此步骤中,纳米片和MDI被‘切割’以进入通道侧壁并启动源极/漏极外延。具有‘原位封盖’的创新型源极/漏极凹槽蚀刻通过在源极/漏极凹槽期间保护栅极硬掩模/栅极间隔物实现了MDI优先。”

第二个关键模块是堆叠源极/漏极底部和顶部触点的形成,它们通过介电隔离垂直分隔。关键步骤是底部触点金属填充和蚀刻,以及随后的介电填充和蚀刻——所有这些都在与MDI堆栈相同的狭小空间内完成。

NaotoHoriguchi:“在从正面开发底部触点时,我们遇到了多重挑战,影响了底部触点电阻并限制了顶部器件源极/漏极形成的工艺窗口。在2024VLSI中,可用于埃米节点,首次展示功能性单片器件我们表明将底部触点形成移至晶圆背面是可行的,尽管与晶圆键合和减薄相关的工艺步骤更多。顶部器件的存活率从11%提高到79%,使背面底部触点形成成为行业中一个有吸引力的选择。目前正在进行研究以确定最佳触点布线方法。”

相关文章《进入埃米级制程工艺,为什么需要CFET?》

编辑:芯智讯-林子来源:imec

1.本站遵循行业规范,任何转载的稿件都会明确标注作者和来源;2.本站的原创文章,请转载时务必注明文章作者和来源,不尊重原创的行为我们将追究责任;3.作者投稿可能会经我们编辑修改或补充。